Module ripple_carry_4_bit(a, b, cin, sum, cout) įull_adder fa0(.a(a).

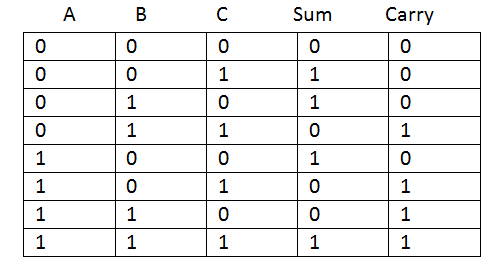

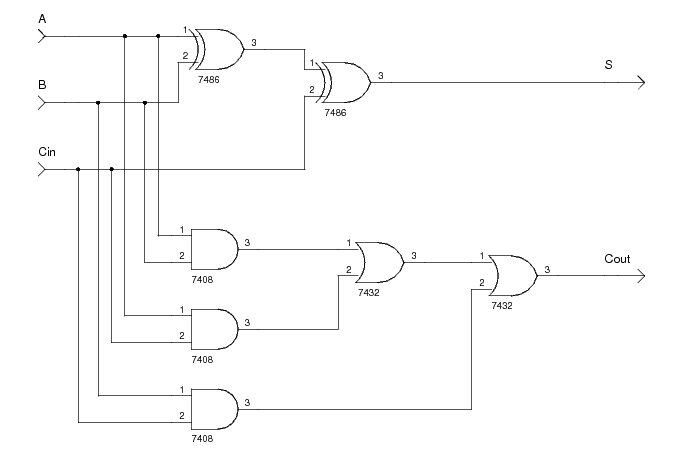

Module pipeline_adder_16bit(clk,reset,a, b, cin, sum, cout) The Verilog Code of 16-bit Pipeline Adder: `timescale 1ns/1ns The Verilog code of 16 bit pipeline adder is given below. To implement this in Verilog we used 4-bit Carry Select Adder Slice as adder slice in Verilog implementation of pipeline adder. The general block diagram of a Pipeline Adder is shown below. The next picture shows the entire schematic of the full adder and its corresponding truth table.

This is a sequential adder, unlike combinational adders like Ripple Carry Adder, Carry Skip Adder, Carry Look-ahead Adder etc needs a storage element and clock. A pipeline adder is a one of the fast adder using the principle of pipelining. Testbench Code- Half Adder timescale 1ns / 1ps ///// // Company: TMP // Create Date: 08:15:45 // Module Name: Half Adder // Project Name: Half Adder.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed